# High Efficiency, 80V, 1.0A Synchronous Step Down Regulator

#### **GENERAL DESCRIPTION**

The SiLM6880/81 is a high efficiency synchronous step down regulator. It can deliver 1A continuous current. The SiLM6880/81 operates over a wide input voltage range from 6V to 80V and integrates the main switch and synchronous switch with very low  $R_{\mbox{\scriptsize DSON}}$  to minimize the power loss and provide a high efficiency solution.

The SiLM6880/81 adopts the constant on time (COT) control architecture to achieve fast transient response. The ultra-low quiescent and diode emulation mode operation improves the efficiency at light load.

The SiLM6880/81 provides internal soft start to limit inrush current. The programmable UVLO pin provide a flexible way to program the startup input voltage and an open drain power good output to indicate the health of the regulator. It also integrates peak and valley current limit protection, thermal shutdown protection.

The SiLM6880/81 operates over -40°C to +150°C junction temperature range and is available in SOP8-EP package.

#### **FEATURES**

- Wide input voltage range: 6V to 80V

- Output current capability: 1A

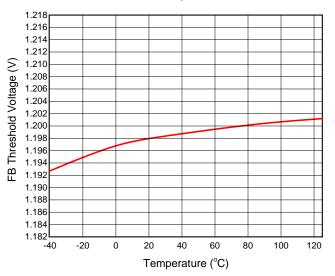

- 1.2V reference voltage with ±1.5% accuracy over temperature

- Integrates low R<sub>DSON</sub> high side/ low side FET:  $600m\Omega/290~m\Omega$

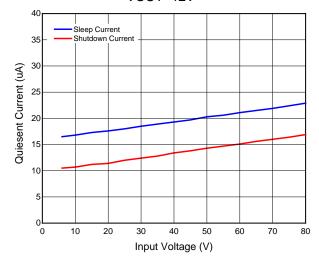

- 20μA quiescent current and 15μA shutdown current

- Constant on time control for fast transient response

- Integrates soft start to limit inrush current

- Open drain power good output

- Programmable UVLO

- Peak and valley current limit protection

- Thermal shutdown protection

- Compact package: SOP8-EP.

#### **APPLICATIONS**

- Telecom supplies

- High-cell-count battery packs (E-bike, E-Scooter)

- Motor drives, drones

- · High voltage post regulator

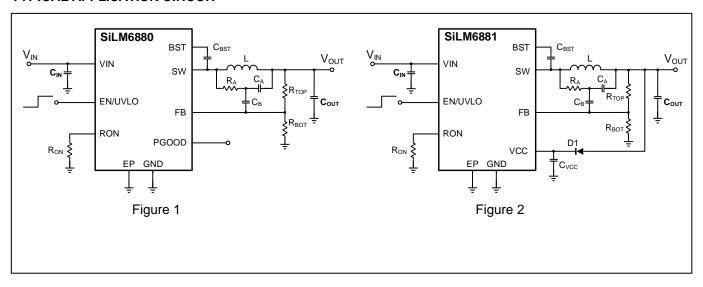

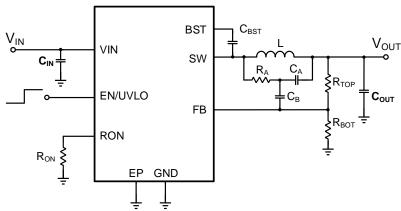

#### TYPICAL APPLICATION CIRCUIT

# **Table of Contents**

| General Description                    | 1  |

|----------------------------------------|----|

| Features                               | 1  |

| Applications                           | 1  |

| Typical Application Circuit            | 1  |

| PIN Configuration                      | 3  |

| PIN Function Descriptions              | 3  |

| Ordering Information                   | 3  |

| Functional Block Diagram               | 4  |

| Absolute Maximum Ratings               | 5  |

| Recommended Operation Conditions       | 5  |

| Electrical Characteristics             | 6  |

| Function Description                   | 8  |

| Control Scheme                         | 10 |

| Output Voltage Setting                 | 10 |

| ON-Timer Setting                       | 10 |

| External Bootstrap Capacitor           | 11 |

| Output Inductor                        | 11 |

| Output Capacitor                       | 11 |

| Input Capacitor                        | 11 |

| Ripple Injection                       | 12 |

| Enable/Under-Voltage Lockout (EN/UVLO) | 12 |

| Internal Regulator                     | 13 |

| Soft Start                             | 13 |

| Current limit                          | 13 |

| Power Good (PGOOD)                     | 14 |

| Working Mode                           | 14 |

| Thermal Protection                     | 14 |

| Package Case Outlines                  | 15 |

| Revision History                       | 16 |

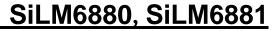

## **PIN CONFIGURATION**

## PIN FUNCTION DESCRIPTIONS

| No.                                                                                                                                      | Pin Name       | Function Description                                                                                                                                                                            |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                                                                                                                                        | GND            | Ground for internal circuits.                                                                                                                                                                   |  |  |  |  |

| 2                                                                                                                                        | VIN            | Power supply input. Connect a bypass capacitor between this pin and GND.                                                                                                                        |  |  |  |  |

| 3                                                                                                                                        | EN/UVLO        | ecision enable input and under-voltage lockout(UVLO) programming pin. An ternal resistor divider can be used to program the UVLO threshold. If the enable is not used, connect this pin to VIN. |  |  |  |  |

| 4                                                                                                                                        | RON            | n-time programming pin. Connect a resistor between this pin and GND to set the ph side switch on-time.                                                                                          |  |  |  |  |

| 5                                                                                                                                        | FB             | Feedback voltage sense input. Connect this pin to a resistor divider from the output voltage.                                                                                                   |  |  |  |  |

| PGOOD (SiLM6880): Power good output (Open Drain). Connect this p power supply through an external pull-up resistor between 10kΩ to 100kΩ |                |                                                                                                                                                                                                 |  |  |  |  |

| VCC (SiLM6881): Internal 5 V LDO output or input voltage for the corplace a 1 μF ceramic capacitor between VCC and GND.                  |                |                                                                                                                                                                                                 |  |  |  |  |

| 7                                                                                                                                        | BST            | Bootstrap gate-drive supply. Required to connect a 3.3 nF 50V X7R ceramic capacitor between BST and SW to bias the internal high-side gate driver.                                              |  |  |  |  |

| 8                                                                                                                                        | SW             | Switching node. Connect to the switching node of the power inductor.                                                                                                                            |  |  |  |  |

|                                                                                                                                          | Exposed<br>Pad | Connect the exposed pad to an external ground plane to improve thermal performance.                                                                                                             |  |  |  |  |

## ORDERING INFORMATION

| Order Part No. | Pin 6 Function | Package | QTY       |

|----------------|----------------|---------|-----------|

| SiLM6880CB-DG  | PGOOD          | SOP8-EP | 2500/Reel |

| SiLM6881CB-DG  | VCC            | SOP8-EP | 2500/Reel |

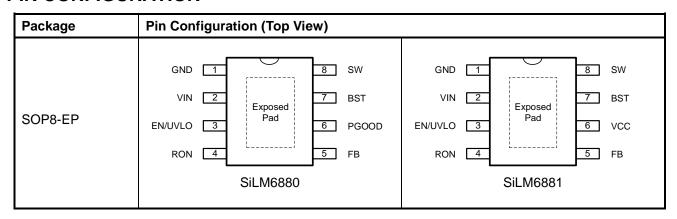

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 3. Functional Block Diagram

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                      | Rating           |

|------------------------------------------------|------------------|

| VIN, EN/UVLO                                   | -0.3V to +85V    |

| SW                                             | -0.3V to +85V    |

| BST                                            | Vsw+6V           |

| RON, FB                                        | -0.3V to +6V     |

| VCC, PGOOD                                     | -0.3V to +30V    |

| External capacitance between BST and SW        | 2.3 nF to 4.0 nF |

| Operation Junction temperature, T <sub>J</sub> | -40°C to 150°C   |

| Storage temperature, Ts                        | -55°C to 150°C   |

#### Note:

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. All voltage parameters are absolute voltages referenced to GND. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATION CONDITIONS

| Symbol          | Definition                     | Min | Nom | Max | Units |

|-----------------|--------------------------------|-----|-----|-----|-------|

| VIN             | Input Voltage                  | 6   |     | 80  | V     |

| lout            | Output Current                 |     | 1   |     | А     |

| ton             | On time                        | 0.1 |     | 10  | μs    |

| f <sub>SW</sub> | Operation switching frequency  |     |     | 500 | kHz   |

| Свѕт            | Capacitance between BST and SW |     | 3.3 |     | nF    |

| TJ              | Junction temperature           | -40 |     | 150 | °C    |

## **ELECTRICAL CHARACTERISTICS**

$V_{\text{IN}} = 48\text{V}$ ,  $V_{\text{OUT}} = 5.0\text{V}$ ,  $T_{\text{J}} = 25^{\circ}\text{C}$  for typical specifications and  $T_{\text{J}} = -40^{\circ}\text{C}$  to +150°C for minimum/maximum specifications, unless otherwise specified.

| Symbol                  | Parameter                               | Condition                      | Min      | Тур  | Max   | Unit |

|-------------------------|-----------------------------------------|--------------------------------|----------|------|-------|------|

| VIN Power S             | Supply                                  |                                | <b>.</b> | 1    |       |      |

| V <sub>VIN</sub>        | Input voltage range on VIN              |                                | 6        |      | 80    | V    |

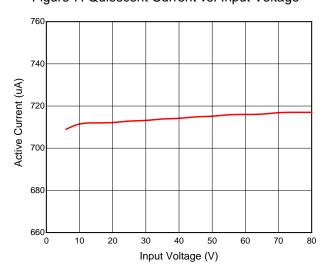

| IVIN_ACTIVE             | Active current on VIN                   | V <sub>EN</sub> = 2.5V         |          | 700  | 900   | μA   |

| IVIN_SLEEP              | Sleep current on VIN                    | $V_{FB} = 1.5V, V_{EN} = 2.5V$ |          | 20   | 35    | μΑ   |

| I <sub>VIN_SD</sub>     | Shutdown current on VIN                 | V <sub>EN</sub> = GND          |          | 15   | 30    | μΑ   |

| $V_{\text{UVLO}}$       | Under voltage lockout threshold         | V <sub>VIN</sub> rising        | 4.7      | 5.2  | 5.7   | V    |

| Vuvlo_HYS               | Under voltage lockout hysteresis        |                                |          | 200  |       | mV   |

| VCC Power               | Supply (SiLM6881 only)                  |                                |          |      |       |      |

| Vvcc                    | Voltage range on VCC                    |                                | 4.5      |      | 30    | V    |

| Vvcc_uvlo_r             | Under voltage lockout threshold         | V <sub>VCC</sub> rising        |          | 4.3  |       | V    |

| Vvcc_uvlo_f             | Under voltage lockout hysteresis        | V <sub>VCC</sub> falling       |          | 4.05 |       | V    |

| Feedback Vo             | oltage                                  |                                |          |      |       |      |

| V <sub>FB</sub>         | Feedback reference voltage              |                                | 1.182    | 1.2  | 1.218 | V    |

| EN/UVLO                 |                                         |                                | 1        | 1    |       |      |

| V <sub>EN_SHDN_R</sub>  | EN shutdown rising threshold            |                                |          |      | 1.1   | V    |

| VEN_SHDN_F              | EN shutdown falling threshold           |                                | 0.4      |      |       | V    |

| V <sub>EN_R</sub>       | EN enable rising threshold              |                                | 1.44     | 1.52 | 1.6   | V    |

| V <sub>EN_HYS</sub>     | EN enable hysteresis                    |                                |          | 100  |       | mV   |

| Bootstrap V             | oltage                                  |                                |          |      |       |      |

| V <sub>BST_UVLO_R</sub> | V <sub>BST</sub> UVLO threshold rising  |                                | 2.2      | 2.7  | 3.2   | V    |

| V <sub>BST_UVLO_F</sub> | V <sub>BST</sub> UVLO threshold falling |                                | 2.0      | 2.5  | 3.0   | V    |

| Power MOS               | FET                                     |                                | 1        | •    |       |      |

| R <sub>DSON_HS</sub>    | High side MOSFET ON Resistance          | Isw = 0.1 A                    |          | 600  |       | mΩ   |

| R <sub>DSON_LS</sub>    | Low side MOSFET ON Resistance           | I <sub>SW</sub> = -0.1 A       |          | 290  |       | mΩ   |

| <b>Current Lim</b>      | it                                      |                                |          |      | _     |      |

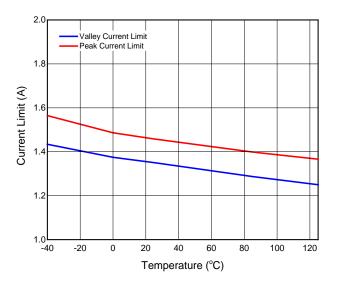

| ILIM_HS_PK              | High side peak current limit            |                                | 1.25     | 1.5  | 1.75  | А    |

| ILIM_LS_PK              | Low side peak current limit             |                                | 1.25     | 1.5  | 1.75  | Α    |

| ILIM_LS_VL              | Low side valley current limit           |                                | 1.0      | 1.2  | 1.4   | А    |

| Soft Start              |                                         |                                |          |      | 1     | 1    |

| tss                     | Soft start time                         |                                | 2        | 3    | 4     | ms   |

# SiLM6880, SiLM6881

| Timing                |                               |                                                  |      |      |      |    |  |

|-----------------------|-------------------------------|--------------------------------------------------|------|------|------|----|--|

| t <sub>MIN_OFF</sub>  | Minimum off time              |                                                  |      | 200  |      | ns |  |

| ton                   | On time                       | $V_{VIN} = 48V$ , $R_{ON} = 100 \text{ k}\Omega$ |      | 833  |      | ns |  |

| Power Good            | Power Good (SiLM6880 only)    |                                                  |      |      |      |    |  |

| V <sub>PG_R</sub>     | Power good rising threshold   |                                                  | 1.09 | 1.14 | 1.18 | V  |  |

| V <sub>PG_F</sub>     | Power good falling threshold  |                                                  | 1.03 | 1.08 | 1.12 | V  |  |

| R <sub>PG</sub>       | Pull down resistance on PGOOD | V <sub>FB</sub> = 1V, IPG = 1mA                  |      | 30   |      | Ω  |  |

| Thermal Shu           | Thermal Shutdown              |                                                  |      |      |      |    |  |

| T <sub>SHDN</sub>     | Thermal Shutdown Threshold    |                                                  |      | 175  |      | °C |  |

| T <sub>SHDN_HYS</sub> | Thermal Shutdown Hysteresis   |                                                  |      | 15   |      | °C |  |

## TYPICAL PERFORMANCE CHARACTERISTICS

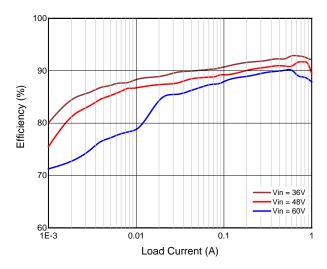

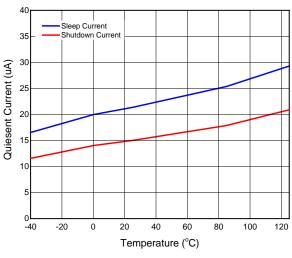

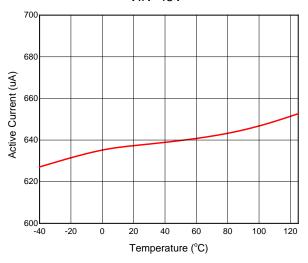

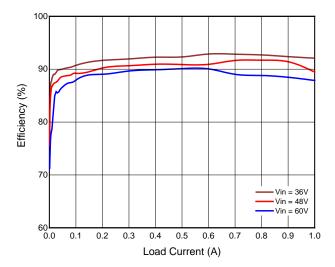

At  $T_A = 25^{\circ}C$ ,  $V_{OUT} = 12V$ ,  $L_O = 68uH$ ,  $R_{RON} = 100k\Omega$ , unless otherwise specified.

Figure 4. Power Conversion Efficiency(Log Scale) VOUT=12V

Figure 6. Quiescent Current vs. Temperature VIN=48V

Figure 5. Power Conversion Efficiency(Linear Scale) VOUT=12V

Figure 7. Quiescent Current vs. Input Voltage

Figure 8. Active Current vs. Temperature VIN=48V

Figure 10. FB Threshold Voltage vs. Temperature

Figure 12. Peak and Valley Current Limit vs. Temperature

Figure 9. Active Current vs. Input Voltage

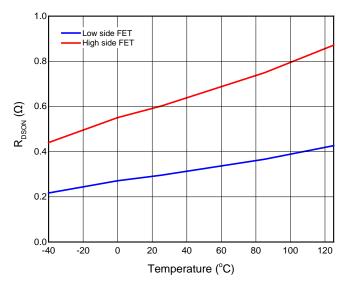

Figure 11. High side and Low side R<sub>DSON</sub> vs. Temperature

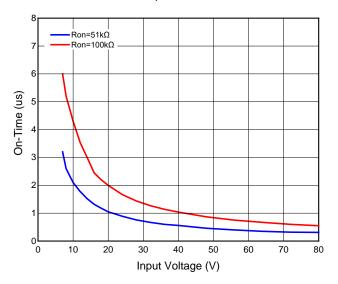

Figure 13. COT On-Time vs. Input Voltage

#### **FUNCTION DESCRIPTION**

#### **Control Scheme**

The SiLM6880/81 adopts a constant on time (COT) control scheme. The COT control scheme sets a fixed on-time ton of the high-side MOSFET using a timing resistor (Ron). The ton is adjusted as input voltage changes and is inversely proportion to input voltage to maintain a fixed frequency when in continuous conduction mode (CCM). After expiration of ton, the high side MOSFET turns off until the feedback pin is equal or below the reference voltage of 1.2 V. In order to maintain stability, the feedback comparator requires a minimal ripple voltage that is in phase with the inductor current during the off-time. Furthermore, this change in feedback voltage during the off-time must be large enough to dominate any noise present at the feedback node. The minimum recommended ripple voltage is 20 mV. Refer to **Ripple Injection** section to ensure stability over the full input voltage range with different configuration.

Diode emulation mode (DEM) prevents negative inductor current, and pulse skipping maintains highest efficiency at light load currents by decreasing the effective switching frequency. DEM operation occurs when the low side MOSFET off as inductor valley current reaches zero. Here, the load current is less than half of the peak-to-peak inductor current ripple in CCM. Turning off the low-side MOSFET at zero current reduces switching loss, and preventing negative current conduction reduces conduction loss. Power conversion efficiency is thus higher in a DEM regulator than an equivalent forced-PWM CCM regulator. With DEM operation, the duration that both power MOSFETs remain off progressively increases as load current decreases. When this idle duration exceeds 15  $\mu$ s, the regulator transitions into an ultra-low loanoge mode, consuming only 10  $\mu$ A quiescent current from the input.

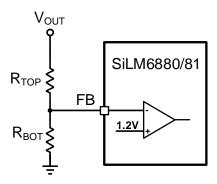

#### **Output Voltage Setting**

Figure 14. Output voltage setting

The SiLM6880/81 voltage regulation loop regulates the output voltage by maintaining the FB voltage equal to the internal reference voltage. The output voltage is setting by an external resistor divider.

$$V_{OUT} = 1.2 \times (1 + \frac{R_{TOP}}{R_{BOT}})$$

#### **ON-Timer Setting**

The on-time of the SiLM6880/81 is determined by the resistance between the RON and ground (Ron), and is inversely proportional to the input voltage, VIN. The inverse relationship with VIN results in a nearly constant frequency as VIN is varied.

The on time can be calculated using the below equation:

$$t_{ON}(\mu s) = \frac{R_{ON} (k\Omega)}{2.5 \times V_{IN}}$$

The R<sub>ON</sub> can be calculated by the below equation:

$$R_{ON}(k\Omega) = \frac{2500 \times V_{OUT}}{f_{SW}(kHz)}$$

ton: the on time of the high side switch.

V<sub>IN</sub>: the input voltage.

Ron: the resistance between the RON and ground.

Vout: the output voltage.

fsw: the switching frequency.

Select Ron for the on-time is greater than  $t_{MIN\_ON}$  (50 ns) and is less than  $t_{MAX\_ON}$  (10µs) over the input voltage for proper operation.

#### **External Bootstrap Capacitor**

The external bootstrap capacitor provides the gate driver voltage for internal high side MOSFET. A high quality 3.3nF 50V X7R ceramic capacitor is recommended to be placed between the BST and SW pin.

#### **Output Inductor**

The inductor value is determined by the operating frequency, input voltage, output voltage, and inductor ripple current. As a guideline, the inductor ripple current,  $\Delta I_L$ , is typically set to 1/3 of the maximum load current. The inductor value can be calculated using the following equation:

$$L = \frac{(V_{IN} - V_{OUT}) \times D}{\Delta I_L \times f_{SW}}$$

#### where:

$V_{\text{IN}}$  is the input voltage.

V<sub>OUT</sub> is the output voltage.

$\Delta I_{\perp}$  is the inductor ripple current.

f<sub>SW</sub> is the switching frequency.

D is the duty cycle.

The saturation current of the inductor must be larger than the peak current limit.

The rms current of the inductor should be greater than the value calculated by the following equation:

$$I_{RMS} = \sqrt{I_{OUT}^2 + \frac{\Delta I_L^2}{12}}$$

#### Where:

I<sub>RMS</sub> is the RMS current of the inductor.

lout is the output current.

$\Delta I_{\perp}$  is the inductor ripple current.

#### **Output Capacitor**

The output capacitor is selected to handle the output ripple noise requirements. Both steady state ripple and transient requirements must be taken into consideration when selecting this capacitor. It is recommended to use an X5R or X7R ceramic capacitor, and capacitance value is greater than  $10\mu F$ .

#### **Input Capacitor**

The input decoupling capacitor attenuates high frequency noise on the input and acts as an energy reservoir. This capacitor should be a ceramic capacitor in the range of 10  $\mu$ F to 47  $\mu$ F and must be placed close to the VIN pin. The loop composed of this input capacitor, high-side MOSFET, and low-side MOSFET must be kept as small as possible. The voltage rating of the input capacitor must be greater than the maximum input voltage. The rms current rating of the input capacitor should be larger than the following equation:

$$I_{RMS\_CIN} = I_{OUT} \times \sqrt{D \times (1-D)}$$

#### Where:

I<sub>RMS\_CIN</sub> is the RMS current on the input capacitor.

I<sub>OUT</sub> is the output current.

D is the duty cycle.

#### Ripple Injection

The SiLM6880/81 adopts a COT control scheme and the PWM timing is based on the output voltage ripple feedback to the FB pin. Typically ripple generation uses an RC network consisting of  $R_A$  and  $C_A$ , and the switch node voltage to generate a triangular ramp that is in-phase with the inductor current. This triangular wave is the AC-coupled into the feedback node with capacitor  $C_B$ . Because this circuit does not use output voltage ripple, it is suited for applications where low output voltage ripple is critical.

Figure 15. Ripple Generation Circuit

The RA, CA, CB shall meet the below equations to make sure the system is stable.

$$C_{A} \ge \frac{10}{f_{sw} \times (R_{TOP} / / R_{BOT})}$$

$$R_{A} \times C_{A} \le \frac{V_{IN} - V_{OUT}}{50 mV} \times t_{ON}$$

$$C_{A} \ge 4 \times C_{B}$$

$$C_{B} \ge \frac{t_{TR}}{3 \times R_{TOP}}$$

Here t<sub>TR</sub> is the recovery time during the transient.

Table 1 lists several typical application cases which recommend the ripple feedback parameter selection.

Table 1. SiLM6880/81 Ripple Generation Parameter Recommendation

| V <sub>IN</sub> | V <sub>оит</sub> | fsw   | Ron  | Inductor | Соит | Rвот | Rтор | RA   | CA   | Св   |

|-----------------|------------------|-------|------|----------|------|------|------|------|------|------|

| (V)             | (V)              | (kHz) | (kΩ) | (uH)     | (uF) | (kΩ) | (kΩ) | (kΩ) | (pF) | (pF) |

| 12              | 5                | 300   | 41.2 | 33       | 44   | 49.9 | 158  | 100  | 820  | 160  |

| 24              | 5                | 300   | 41.2 | 33       | 44   | 49.9 | 158  | 330  | 820  | 160  |

| 48              | 5                | 300   | 41.2 | 33       | 44   | 49.9 | 158  | 360  | 820  | 160  |

| 24              | 12               | 300   | 100  | 68       | 44   | 49.9 | 449  | 120  | 3300 | 56   |

| 48              | 12               | 300   | 100  | 68       | 44   | 49.9 | 449  | 160  | 3300 | 56   |

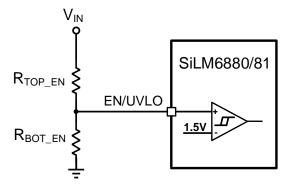

#### Enable/Under-Voltage Lockout (EN/UVLO)

The SiLM6880/81 contains a dual-level EN/UVLO circuit. When the EN/UVLO voltage is below 1.1 V (typical), the regulator is in a low-current shutdown mode and the input current ( $I_{VIN\_SD}$ ) is dropped down to 15  $\mu$ A. When the voltage is greater than 1.1 V but less than 1.5 V (typical), the regulator is in standby mode. In standby mode the internal bias regulator is active while the control circuit is disabled. When the voltage exceeds the rising threshold of 1.5 V (typical), normal operation begins.

The SiLM6880/81 also provides an UVLO programmable function. An external resistor divider from VIN to GND can be used to set the minimum operating voltage of the regulator as shown in Figure 16. Use below equation to calculate the input UVLO turn on and turn off voltages:

$$V_{\text{IN\_ON}} = 1.5 \times (1 + \frac{R_{\text{TOP\_EN}}}{R_{\text{BOT\_EN}}})$$

$$V_{\text{IN\_OFF}} = 1.4 \times (1 + \frac{R_{\text{TOP\_EN}}}{R_{\text{BOT\_EN}}})$$

Figure 16. Input UVLO threshold program

If input UVLO is not required, the EN/UVLO pin can be used as an enable input driving by a logic signal or connecting it directly to VIN. If EN/UVLO is directly connected to VIN, the regulator begins switching as soon as the internal bias rails are active.

#### **Internal Regulator**

The SiLM6880 integrates an internal linear regulator (VDD) that is powered from VIN with a nominal output of 5 V, eliminating the need for an external capacitor to stabilize the linear regulator. The internal VDD regulator supplies current to internal circuit blocks including the synchronous FET driver and logic circuits.

The SiLM6881 has a VCC pin which provides another input to the internal VDD regulator. When the VCC voltage is larger than 4.3V, the power supply of internal VDD regulator is switched to VCC. This feature reduces power consumption on the VDD regulator like connecting the VCC to the output of the buck as shown in Figure 2.

#### Soft Start

The SiLM6880/81 integrates an internal soft-start circuit to control the output voltage ramps up gradually, thereby reducing inrush current during the start up. The soft-start time is internally set to 3 ms.

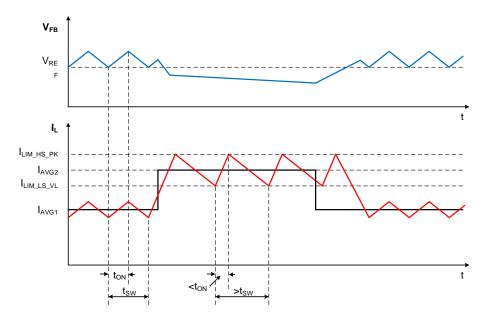

#### **Current limit**

The SiLM6880/81 integrates overcurrent protection with cycle-by-cycle current limiting of the peak inductor current. The high-side MOSFET current is sensed and compared every switching cycle to the peak current limit threshold.

To protect the regulator from potential current runaway conditions, the SiLM6880/81 includes a fold-back valley current limit feature that is enabled if a peak current limit is detected. As shown in Figure 17, if the peak current in the high-side MOSFET exceeds the peak current limit threshold (1.5 A typical), the present cycle is immediately terminated regardless of the programmed on-time (ton), the high-side MOSFET is turned off and the fold-back valley current limit is activated. The low-side MOSFET remains on until the inductor current drops below this fold-back valley current limit (1.2A typical), after which the next on-pulse is initiated. This method folds back the switching frequency to prevent overheating and limits the average output current to less than 1.5 A to ensure proper short-circuit and heavy-load protection of the SiLM6880/81.

Current is sensed after a leading-edge blanking time following the high-side MOSFET turn on transition. The propagation delay of the current limit comparator is 100 ns. During high step-down conditions when the on-time is less than 100 ns, a back-up peak current limit comparator in the low-side MOSFET also set at 1.5 A will enable the fold-back valley current limit set at 1.2 A. This current limit scheme enables ultra-low duty-cycle operation while ensuring robust protection of the regulator.

Figure 17. Current limit diagram

#### **Power Good (PGOOD)**

The power good (PGOOD) pin is an active high, open drain output that indicates if the regulator output voltage is within regulation. High indicates that the voltage at the FB pin (and, hence, the output voltage) is above 95% of the reference voltage. Low indicates that the voltage at the FB pin (and, hence, the output voltage) is below 90% of the reference voltage. PGOOD pin requires a pull-up resistor to a DC supply not greater than 30 V. The typical range of pull-up resistance is 10 k $\Omega$  to 100 k $\Omega$ .

#### **Working Mode**

There are three working modes in the SiLM6880/81: active mode, sleep mode and shutdown mode.

The SiLM6880/81 works in shutdown mode when the voltage on the EN/UVLO pin is below 1.1 V. Both the internal linear regulator and the switching regulator are off. The quiescent current in shutdown mode drops to 15µA.

The SiLM6880/81 works in active mode when the voltage on the EN/UVLO pin is above the enable rising threshold (1.5V typical) and input voltage is above its UVLO threshold. In COT active mode, the SiLM6880/81 is in one of three modes depending on the load current:

- CCM with fixed switching frequency when load current is above half of the peak-to-peak inductor current ripple

- Pulse skipping and diode emulation mode (DEM) when the load current is less than half of the peak-to-peak inductor current ripple in CCM operation

- Current limit CCM with peak and valley current limit protection when an overcurrent condition is applied at the output.

At the light load, as the frequency of operation decreases and  $V_{FB}$  remains above 1.2 V with the output capacitor sourcing the load current for greater than 15  $\mu$ s, the SiLM6880/81 enters sleep mode. The input quiescent current ( $I_{VIN\_SLEEP}$ ) required by the SiLM6880/81 decreases to 20  $\mu$ A in sleep mode, improving the light-load efficiency of the regulator. In the sleep mode all internal controller circuits are turned off to ensure very low current consumption. Such low  $I_{VIN\_SLEEP}$  renders the SiLM6880/81 as the best option to extend operating lifetime for off-battery applications. The FB comparator and internal bias rail are active to detect when the FB voltage drops below the internal reference and the regulator transitions out of sleep mode into active mode. There is a 9  $\mu$ s wake-up delay from sleep to active states.

#### **Thermal Protection**

In the event that the SiLM6880/81 junction temperature exceeds 175°C, the thermal shutdown circuit turns off the regulator. A 15°C hysteresis is included so that the SiLM6880/81 does not recover from thermal shutdown until the on-chip temperature drops below 160°C. Upon recovery, soft start is initiated prior to normal operation.

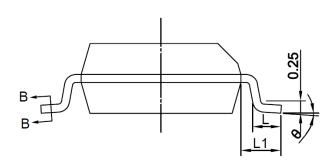

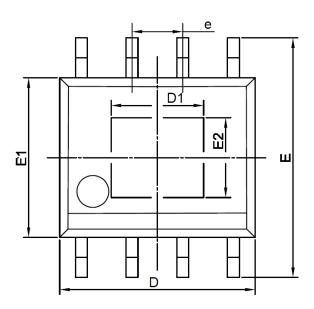

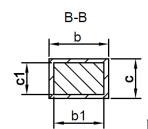

# **PACKAGE CASE OUTLINES**

| Dimension | IVIIN | TYP  | MAX  |  |  |  |

|-----------|-------|------|------|--|--|--|

| Α         | -     | -    | 1.70 |  |  |  |

| A1        | 0     | -    | 0.15 |  |  |  |

| A2        | 1.25  | -    | -    |  |  |  |

| L         | 0.40  | 0.84 | 1.27 |  |  |  |

| L1        | -     | 1.04 | -    |  |  |  |

| θ         | 0°    | -    | 8°   |  |  |  |

| b         | 0.31  | -    | 0.51 |  |  |  |

| b1        | 0.28  | -    | 0.48 |  |  |  |

| С         | 0.10  | -    | 0.25 |  |  |  |

| c1        | 0.10  | -    | 0.25 |  |  |  |

| D         | 4.70  | 4.90 | 5.10 |  |  |  |

| D1        | 1.50  | 3.30 | 3.40 |  |  |  |

| Е         | 5.80  | 6.00 | 6.20 |  |  |  |

| E1        | 3.80  | 3.90 | 4.05 |  |  |  |

| E2        | 1.00  | 2.40 | 2.50 |  |  |  |

| е         | 1.02  | 1.27 | 1.52 |  |  |  |

| Unit: mm  |       |      |      |  |  |  |

Figure 18. SOP8-EP Outline Dimensions

## **REVISION HISTORY**

Note: page numbers for previous revisions may differ from page numbers in current version

| Page or Item Subjects (major changes since previous revision) |                 |  |  |  |  |

|---------------------------------------------------------------|-----------------|--|--|--|--|

| Datasheet Rev 1.0: 2024-07-05                                 |                 |  |  |  |  |

| Whole document                                                | Initial release |  |  |  |  |