# Dual Channel 10A, 5.0kV<sub>RMS</sub> Isolated Gate Driver

### **GENERAL DESCRIPTION**

The SiLM8260A is an isolated dual channel gate driver with 10A source and 10A sink peak output current. The SiLM8260A are configured as high-side/low-side drivers with over-lap protection and programmable dead time feature. Pulling high the DIS pin shuts down both outputs simultaneously, and allows for normal operation when the DIS pin is open or pulled low. As a fail-safe measure, primary-side logic failures force both outputs low. The internal clamp feature to prevent false turn on caused by miller current.

The VDDA and VDDB supply voltage are up to 30 V. A wide input VDDI range from 3.5 V to 18 V makes the driver suitable for interfacing with both analog and digital controllers. All the supply voltage pins have under voltage lock-out (UVLO) protection.

The SiLM8260A has 5.0kV<sub>RMS</sub> isolation in SOP18W package per UL1577.

High CMTI, low propagation delay, small pulse width distortion and higher operation temperature makes the SiLM8260A ideal for use in all types of motor drives, solar inverters, industrial power supplies, and appliances.

#### **FEATURE**

- 10A peak source/sink current

- 80ns (Typ.) propagation delay

- 150kV/us (Min.) common mode transient immunity (CMTI)

- Input side supply range from 3.5V to 18V

- Driver side supply range from 4V to 30V

- 12.5V, 8.5V, 5.5V and 3.5V UVLO Options

- 5V reverse polarity voltage handling capability on input stage

- 1850V functional isolation between two drivers

- Operating temperature: –40°C to +125°C

- · Safety certifications:

- 5kV<sub>RMS</sub> isolation for 1 minute per UL 1577 with SOP18W package

- CQC certification per GB4943.1-2011

- DIN VDE 0884-17: 2021-10

#### **APPLICATION**

- AC/DC or DC/DC power supplies in server, telecom and industry

- DC/AC solar inverters

- EV battery charging

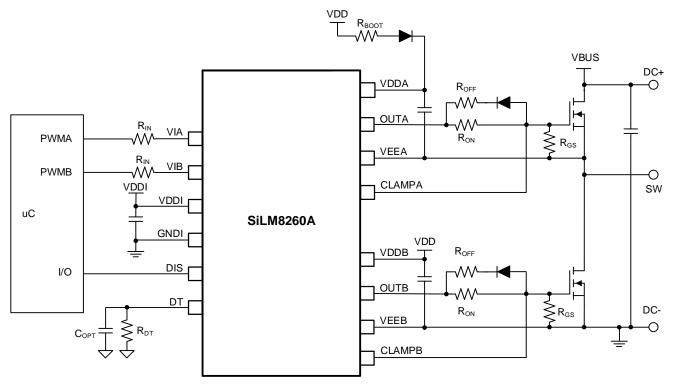

### **APPLICATION CIRCUIT**

Figure 1. SiLM8260A Application Circuit

# **Table of Contents**

| General Description                           | 1  |

|-----------------------------------------------|----|

| Feature                                       | 1  |

| Application                                   | 1  |

| Application Circuit                           | 1  |

| PIN Configuration                             | 3  |

| PIN Description                               | 4  |

| Functional Block Diagram                      | 5  |

| Ordering Information                          | 6  |

| Absolute Maximum Ratings <sup>1</sup>         | 7  |

| Recommended Operation Conditions <sup>1</sup> | 7  |

| ESD Ratings                                   | 7  |

| Thermal Information                           | 7  |

| Package Specifications                        | 9  |

| Insulation Specifications                     | 9  |

| Safety Related Certifications                 | 10 |

| Electrical Characteristics (DC)               | 11 |

| Switching Characteristics (AC)                | 12 |

| Parameter Measurement Information             | 13 |

| Propagation Delay and Pulse Width Distortion  | 13 |

| Rise and Fall Time Testing                    | 13 |

| CMTI Testing                                  | 13 |

| Feature Description                           | 14 |

| Under Voltage Lockout                         | 14 |

| Disable Input Function                        | 14 |

| Control Input and Output Logic                | 14 |

| Dead-time Program                             | 14 |

| Internal Active Miller Clamp                  | 15 |

| Active Output Pulldown                        | 15 |

| Application Information                       | 16 |

| Package Case Outlines                         | 17 |

| Revision History                              | 18 |

# **PIN CONFIGURATION**

| NC | Package | Pin Configuration (Top View) |                                                          |  |  |

|----|---------|------------------------------|----------------------------------------------------------|--|--|

|    |         | NC                           | 18 VEEA  17 CLAMPA  16 OUTA  15 VDDA  14 VEEB  13 CLAMPB |  |  |

# **PIN DESCRIPTION**

| No. | Pin Name | Description                                                                                                                                                                                                           |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | NC       | No connection                                                                                                                                                                                                         |

| 2   | VIA      | Input of driver A. The output of driver A is in phase with the input. This pin is pulled low internally if left open. Recommend to connect this pin to ground if not used for better noise immunity.                  |

| 3   | VIB      | Input of driver B. The output of driver B is in phase with the input. This pin is pulled low internally if left open. Recommend to connect this pin to ground if not used for better noise immunity.                  |

| 4   | NC       | No connection                                                                                                                                                                                                         |

| 5   | DIS      | Device disable input. When DIS pin is high, both driver is disabled and driver output is low. When DIS pin is low, it allows the device to perform in normal operation.                                               |

| 6   | DT       | Dead time programming input. Connect a resistor between DT and GNDI to program the dead time. A bypassing capacitor, 2.2nF or greater, is recommended to be put between DT and GNDI to achieve better noise immunity. |

| 7   | GNDI     | Input power ground.                                                                                                                                                                                                   |

| 8   | NC       | No connection                                                                                                                                                                                                         |

| 9   | VDDI     | Input power supply. A local low ESR and ESL capacitor should be connected between VDDI and GNDI.                                                                                                                      |

| 10  | NC       | No connection                                                                                                                                                                                                         |

| 11  | VDDB     | Power supply of driver B. A local low ESR and ESL capacitor should be connected between VDDB and VEEB.                                                                                                                |

| 12  | OUTB     | Output of driver B.                                                                                                                                                                                                   |

| 13  | CLAMPB   | Active Miller clamp input of driver B used to prevent false turn-on of the power switches                                                                                                                             |

| 14  | VEEB     | Power ground of driver B.                                                                                                                                                                                             |

| 15  | VDDA     | Power supply of driver A. A local low ESR and ESL capacitor should be connected between VDDA and VEEA.                                                                                                                |

| 16  | OUTA     | Output of driver A.                                                                                                                                                                                                   |

| 17  | CLAMPA   | Active Miller clamp input of driver A used to prevent false turn-on of the power switches                                                                                                                             |

| 18  | VEEA     | Power ground of driver A.                                                                                                                                                                                             |

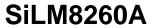

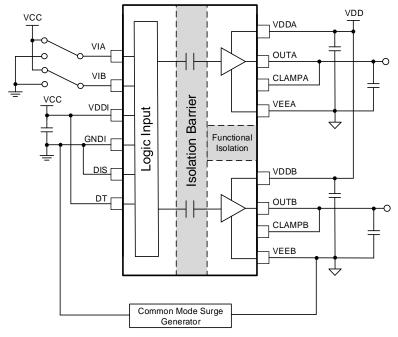

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. SiLM8260A Functional Block Diagram

# **ORDERING INFORMATION**

| Order Part No.  | VCC2 UVLO   | Package | QTY       |

|-----------------|-------------|---------|-----------|

| SiLM8260ADCS-DG | 12.5V/11.5V | SOP18W  | 1500/Reel |

| SiLM8260ABCS-DG | 8.5V/7.5V   | SOP18W  | 1500/Reel |

| SiLM8260AACS-DG | 5.5V/5V     | SOP18W  | 1500/Reel |

| SiLM8260AGCS-DG | 3.5V/3V     | SOP18W  | 1500/Reel |

## **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| Symbol                                               | Definition                                                  | Min  | Max                                             | Unit |

|------------------------------------------------------|-------------------------------------------------------------|------|-------------------------------------------------|------|

| V <sub>DDI</sub>                                     | Input Power Supply Voltage                                  | -0.3 | 20                                              | V    |

| V <sub>IA</sub> , V <sub>IB</sub> , V <sub>DIS</sub> | Input Signal Voltage                                        | -7   | 20                                              | V    |

| V <sub>DDA</sub> , V <sub>DDB</sub>                  | Driver Power Supply                                         | -0.3 | 35                                              | V    |

| Vоита <b>.</b> Vоитв                                 | Driver Output Voltage                                       | -0.3 | V <sub>DDA</sub> +0.3,<br>V <sub>DDB</sub> +0.3 | V    |

| VOUTA, VOUTB                                         | Driver Output Voltage, Transient for 200ns <sup>2</sup>     | -3   | V <sub>DDA</sub> +0.3,<br>V <sub>DDB</sub> +0.3 | V    |

| Vclampa, Vclampb                                     | Internal Clamping Voltage                                   | -0.3 | V <sub>DDA</sub> +0.3,<br>V <sub>DDB</sub> +0.3 | V    |

| V CLAWIFA, V CLAWIFB                                 | Internal Clamping Voltage, Transient for 200ns <sup>2</sup> | -3   | V <sub>DDA</sub> +0.3,<br>V <sub>DDB</sub> +0.3 | V    |

| V <sub>ch2ch</sub>                                   | Channel to Channel Internal Isolation Voltage               |      | 1850                                            | V    |

| ΤJ                                                   | Junction Temperature                                        | -40  | 150                                             | °C   |

| Ts                                                   | Storage Temperature                                         | -55  | 150                                             | °C   |

### **RECOMMENDED OPERATION CONDITIONS<sup>1</sup>**

| Symbol                              | Definition                                | Min  | Max | Unit |

|-------------------------------------|-------------------------------------------|------|-----|------|

| V <sub>DDI</sub>                    | Input Power Supply Voltage                | 3.5  | 18  | V    |

| VIA, VIB, VDIS                      | Input Signal Voltage                      | -5   | 18  | V    |

|                                     | Driver supply voltage (12.5V UVLO option) | 13.6 | 30  | V    |

| V <sub>DDA</sub> , V <sub>DDB</sub> | Driver supply voltage (8.5V UVLO option)  | 9.1  | 30  | V    |

| V DDA, V DDB                        | Driver supply voltage (5.5V UVLO option)  | 6.0  | 30  | V    |

|                                     | Driver supply voltage (3.5V UVLO option)  | 4.0  | 30  | V    |

| R <sub>DT</sub>                     | Resistance range on DT                    | 5    | 220 | kΩ   |

| Срт                                 | Capacitance on DT                         |      | 10  | nF   |

| Та                                  | Ambient Temperature                       | -40  | 125 | °C   |

### **ESD RATINGS**

| Symbol           | Definition | Value | Units |

|------------------|------------|-------|-------|

| V <sub>ESD</sub> | НВМ        | ±4000 | V     |

| VEGD             | CDM        | ±2000 | •     |

Note 1: V<sub>DDI</sub>, V<sub>IA</sub>, V<sub>IB</sub>, V<sub>DIS</sub> are reference to GNDI; V<sub>DDA</sub>, V<sub>OUTA</sub>, V<sub>CLAMPA</sub> are referenced to VEEA; V<sub>DDB</sub>, V<sub>OUTB</sub>, V<sub>CLAMPB</sub> are referenced to VEEB; Note 2: Values are verified by characterization on bench

# THERMAL INFORMATION

| Symbol            | Definition                                | Value | Unit |

|-------------------|-------------------------------------------|-------|------|

| Reja              | Junction to ambient thermal resistance    | 80    | °C/W |

| <b>R</b> өJC(ТОР) | Junction to case (top) thermal resistance | 35    | °C/W |

## **PACKAGE SPECIFICATIONS**

| Symbol          | Definition                              | Min. | Тур.             | Max. | Units |

|-----------------|-----------------------------------------|------|------------------|------|-------|

| Rio             | Resistance (Input Side to Output Side)  |      | 10 <sup>12</sup> |      | Ω     |

| C <sub>IO</sub> | Capacitance (Input Side to Output Side) |      | 1.8              |      | pF    |

### **INSULATION SPECIFICATIONS**

| Symbol                | Definition                                | Test Condition                                                                                                                     | Value     | Units            |

|-----------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|

| CLR                   | External clearance                        | Shortest terminal to terminal distance through air                                                                                 | 8.0       | mm               |

| CPG                   | External creepage                         | Shortest terminal to terminal distance across the package surface                                                                  | 8.0       | mm               |

| DTI                   | Distance through the insulation           | Minimum internal gap                                                                                                               | >16       | um               |

| СТІ                   | Comparative tracking index                | DIN EN 60112 (VDE 0303-11),<br>IEC 60112                                                                                           | >600      | V                |

|                       | Material Group                            |                                                                                                                                    | I         |                  |

|                       |                                           | Rated mains voltages ≤150Vrms                                                                                                      | IV        |                  |

|                       | Overvoltage category                      | Rated mains voltages ≤300Vrms                                                                                                      | IV        |                  |

|                       | Overvollage callegory                     | Rated mains voltages ≤600Vrms                                                                                                      | III       |                  |

|                       |                                           | Rated mains voltages ≤1000Vrms                                                                                                     | II        |                  |

| DIN VDE               | D884-17 <sup>(1)</sup>                    |                                                                                                                                    |           |                  |

| V <sub>IORM</sub>     | Maximum repetitive peak isolation voltage |                                                                                                                                    | 1414      | V <sub>PK</sub>  |

| V <sub>IOWM</sub>     | Maximum isolation working                 | AC voltage (Sine wave)                                                                                                             | 1000      | V <sub>RMS</sub> |

| VIOWW                 | voltage                                   | DC voltage                                                                                                                         | 1414      | V <sub>DC</sub>  |

| V <sub>ІОТМ</sub>     | Maximum transient isolation voltage       | 60s                                                                                                                                | 7000      | V <sub>PK</sub>  |

| V <sub>IOSM</sub>     | Maximum surge isolation voltage           | Test method per IEC62368,<br>1.2/50us waveform, V <sub>TEST</sub> =1.6 x<br>V <sub>IOSM</sub>                                      | 6250      | V <sub>PK</sub>  |

| <b>q</b> pd           | Apparent charge                           | Method b2: $V_{pd(m)}$ =1.875 x $V_{IORM}$ , $tm$ =1 s                                                                             | ≤5        | рС               |

|                       | Climatic Category                         |                                                                                                                                    | 40/125/21 |                  |

|                       | Pollution Degree                          |                                                                                                                                    | 2         |                  |

| UL1577 <sup>(1)</sup> | 1                                         |                                                                                                                                    |           | ı                |

| Viso                  | Withstand Isolation Voltage               | V <sub>TEST</sub> =V <sub>ISO</sub> , t=60s (qualification),<br>V <sub>TEST</sub> =1.2 x V <sub>ISO</sub> , t=1s (100% production) | 5000      | V <sub>RMS</sub> |

Note 1: Certification pending

# **SAFETY RELATED CERTIFICATIONS**

| VDE                      | UL                                       | CQC                                                         |

|--------------------------|------------------------------------------|-------------------------------------------------------------|

| DIN VDE 0884-17: 2021-10 | UL 1577 component recognition program    | Certified according to<br>GB4943.1-2011                     |

| Reinforced Insulation    | Single protection, 5000 V <sub>RMS</sub> | Reinforced insulation,<br>Altitude≤ 5000m, Tropical climate |

| Certification Pending    | File number: E521801-20210610            | Certification Pending                                       |

## **ELECTRICAL CHARACTERISTICS (DC)**

$V_{DDI}=5~V,~0.1\mu F~capacitor~from~VDDI~to~GNDI,~V_{DDA}=V_{DDB}=15V,~1\mu F~capacitor~from~VDDA~and~VDDB~to~VEEA~and~VEEB,~T_A=-40^{\circ}C~to~+125^{\circ}C,~unless~otherwise~specified.$

| Symbol                                    | Parameter                                                 | Condition                                                   | Min  | Тур  | Max  | Unit |

|-------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------|------|------|------|------|

| Input Power Su                            | pply                                                      |                                                             |      |      |      |      |

| V <sub>DDI</sub>                          | Input Supply Voltage                                      |                                                             | 3.5  |      | 18   | V    |

| Vuvlo_vddi_r                              | VDDI UVLO Rising                                          |                                                             | 2.55 | 2.7  | 2.85 | V    |

| Vuvlo_vddi_f                              | VDDI UVLO Falling                                         |                                                             | 2.35 | 2.5  | 2.65 | V    |

| V <sub>UVLO_HYS</sub>                     | VDDI UVLO Hysteresis                                      |                                                             |      | 0.2  |      | V    |

|                                           | Quiescent Current                                         | V <sub>IA</sub> = 0V, V <sub>IB</sub> = 0V                  | 1.4  | 2    | 2.6  | mA   |

| IVDDI                                     | Operation Current                                         | f <sub>sw</sub> = 50kHz, (50% Duty<br>Cycle), both channels | 2.17 | 3.1  | 4.03 | mA   |

| Logic Interface                           | 1                                                         |                                                             | 1    |      |      |      |

| VIH                                       | High Level Input Threshold<br>Voltage at VIA, VIB and DIS |                                                             |      | 2.5  | 3    | V    |

| V <sub>IL</sub>                           | Low Level Input Threshold<br>Voltage at VIA, VIB and DIS  |                                                             | 1    | 1.4  |      | V    |

| Vihys                                     | Hysteresis Voltage at VIA, VIB and DIS                    |                                                             |      | 1.1  |      | V    |

| R <sub>PD</sub>                           | Pull down Resistance on VIA,VIB and DIS                   |                                                             | 126  | 180  | 235  | kΩ   |

| Driver Power S                            | upply                                                     | ,                                                           |      |      |      |      |

|                                           |                                                           | 3.5V UVLO Version                                           | 3.2  | 3.5  | 3.8  | V    |

| Vuvlo_vdda_r,                             | VDDA, VDDB UVLO Rising                                    | 5.5V UVLO Version                                           | 5.1  | 5.5  | 5.9  | V    |

| $V_{\text{UVLO\_VDDB\_R}}$                |                                                           | 8.5V UVLO Version                                           | 8    | 8.5  | 9    | V    |

|                                           |                                                           | 12.5V UVLO Version                                          | 11.5 | 12.5 | 13.5 | V    |

|                                           |                                                           | 3.5V UVLO Version                                           | 2.7  | 3    | 3.3  | V    |

| Vuvlo_vdda_f,                             | VDDA, VDDB UVLO Falling                                   | 5.5V UVLO Version                                           | 4.6  | 5    | 5.4  | V    |

| $V_{\text{UVLO\_VDDB\_F}}$                | VDDA, VDDB OVEO I alling                                  | 8.5V UVLO Version                                           | 7    | 7.5  | 8    | V    |

|                                           |                                                           | 12.5V UVLO Version                                          | 10.5 | 11.5 | 12.5 | V    |

|                                           |                                                           | 3.5V UVLO Version                                           |      | 0.5  |      | V    |

| Vuvlo_vdda_hys,<br>Vuvlo_vddb_hys         | VDDA, VDDB UVLO                                           | 5.5V UVLO Version                                           |      | 0.5  |      | V    |

|                                           | Hysteresis                                                | 8.5V UVLO Version                                           |      | 1    |      | V    |

|                                           |                                                           | 12.5V UVLO Version                                          |      | 1    |      | V    |

|                                           | VDDA/D Ocionant Comment                                   |                                                             |      | 4.4  | 2.1  | mA   |

| I <sub>VDDA_Q</sub> , I <sub>VDDB_Q</sub> | VDDA/B Quiescent Current, per Channel                     | $V_{IA} = 0V, V_{IB} = 0V$                                  |      | 1.4  | 2.1  | ША   |

| Symbol                | Parameter                          | Condition Mir                           |     | Тур | Max | Unit |

|-----------------------|------------------------------------|-----------------------------------------|-----|-----|-----|------|

| OUTPUT                | ı                                  |                                         |     |     |     |      |

| Іон                   | Peak Source Current                |                                         |     | 10  |     | Α    |

| loL                   | Peak Sink Current                  |                                         |     | 10  |     | Α    |

| V <sub>OH</sub>       | High Level Output Voltage          | I <sub>O</sub> =-20mA                   |     | 8   | 15  | mV   |

| VoL                   | Low Level Output Voltage           | I <sub>O</sub> =20mA                    |     | 8   | 15  | mV   |

| Voutsd                | Active pulldown voltage on OUTA(B) | I <sub>OUT</sub> =0.1A, VDDA(B)<br>Open |     | 1.8 | 2.5 | V    |

| Active Miller Cl      | amp                                |                                         |     | l.  |     |      |

| I <sub>CLAMP</sub>    | Clamp low level current            |                                         |     | 10  |     | Α    |

| VCLAMP                | Clamp low level voltage            | I <sub>CLAMP</sub> =20mA                |     | 7   | 13  | mV   |

| V <sub>CLAMP-TH</sub> | Clamp threshold voltage            |                                         | 1.8 | 2   | 2.2 | V    |

| Dead Time             |                                    |                                         |     | 1   | 1   |      |

| t <sub>DT</sub>       | Dead time                          | R <sub>DT</sub> =20kΩ                   | 160 | 200 | 250 | ns   |

# **SWITCHING CHARACTERISTICS (AC)**

$V_{DDI}$  = 5 V, 0.1µF capacitor from VDDI to GNDI,  $V_{DDA}$  =  $V_{DDB}$  =15V, 1µF capacitor from VDDA and VDDB to VEEA and VEEB,  $T_A$  =  $-40^{\circ}$ C to +125°C, unless otherwise specified.

| Symbol              | Parameter                                          | Condition                                                                 | Min | Тур | Max | Unit  |

|---------------------|----------------------------------------------------|---------------------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>PLH</sub>    | Propagation delay, Low to High                     |                                                                           |     | 80  | 130 | ns    |

| t <sub>PHL</sub>    | Propagation delay, High to Low                     | C <sub>LOAD</sub> =1nF, f <sub>sw</sub> =20kHz,                           |     | 80  | 130 | ns    |

| t <sub>PWD</sub>    | Pulse Width Distortion                             | (50% Duty Cycle)                                                          |     |     | 40  | ns    |

| t <sub>DM</sub>     | Propagation Delay Matching between OUTA and OUTB   |                                                                           |     |     | 40  | ns    |

| t <sub>PW_MIN</sub> | Minimum pulse width                                | Output off for less than minimum pulse width                              |     | 40  | 70  | ns    |

| tr                  | Turn on rise time                                  | C <sub>LOAD</sub> =1nF                                                    |     |     | 15  | ns    |

| tf                  | Turn off fall time                                 | C <sub>LOAD</sub> =1nF                                                    |     |     | 15  | ns    |

| tuvlo_rec_vddi      | VDDI UVLO Recovery Delay                           |                                                                           |     | 15  |     | us    |

| tuvlo_rec_vdda(b)   | VDDA, VDDB UVLO Recovery Delay                     |                                                                           |     | 25  | 40  | us    |

| CMTI <sub>H</sub>   | Output High Level Common Mode Transient Immunity   | V <sub>CM</sub> =1000V, V <sub>DDA(B)</sub> =15V,<br>T <sub>A</sub> =25°C | 150 | 200 |     | kV/us |

| CMTI∟               | Output Low Level Common<br>Mode Transient Immunity | V <sub>CM</sub> =1000V, V <sub>DDA(B)</sub> =15V,<br>T <sub>A</sub> =25°C | 150 | 200 |     | kV/us |

### PARAMETER MEASUREMENT INFORMATION

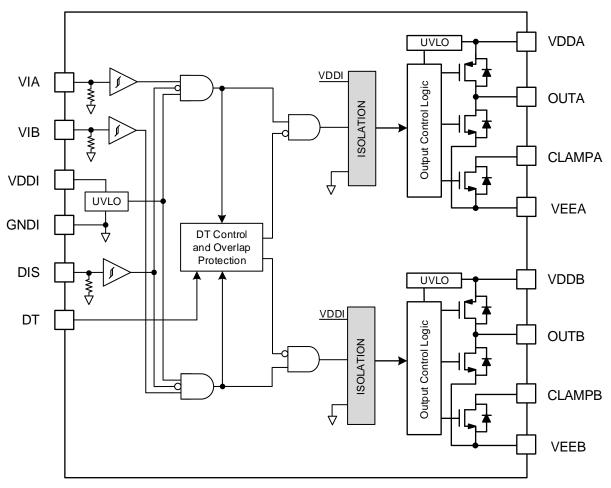

### **Propagation Delay and Pulse Width Distortion**

Figure 3 shows the timing diagram of the propagation delay  $t_{PDLH}$  and  $t_{PDHL}$ , pulse distortion  $t_{PWD}$  and delay matching  $t_{DM}$  from the input  $V_{IA}$  and  $V_{IB}$ . Short the DT pin to VDDI to disable the dead time function.

Figure 3. Propagation Delay and Pulse Width Distortion

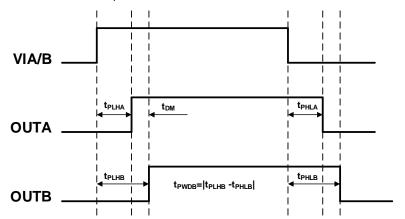

### Rise and Fall Time Testing

Figure 4 shows the criteria for measuring rise time (t<sub>f</sub>) and fall time (t<sub>f</sub>).

Figure 4. Turn On Rise Time and Turn Off Fall Time

### **CMTI Testing**

Figure 5 is the simplified diagram of the CMTI testing. Common mode voltage is set to 1000V.

Figure 5. CMTI Test Circuit

### FEATURE DESCRIPTION

SiLM8260A is a flexible dual channel isolated gate driver that can drive IGBTs and MOSFETs. It has 10A peak output current capability with maxim output driver supply voltage of 30V. SiLM8260A has many features that allow it to integrate well with control circuitry and protect the gates it drives such as: resistor programmable dead time control, an DIS pin, and under voltage lock out (UVLO) for both input and output voltages.

### **Under Voltage Lockout**

The SiLM8260A has under voltage lock out (UVLO) protection feature on each driver power supply voltage between the VDDA (VDDB) and VEEA (VEEB) pins. When the VDDx voltage is lower than  $V_{UVLO\_VDDX\_R}$ , during device start up or lower than  $V_{UVLO\_VDDX\_F}$ , after start up, the VDDA (VDDB) UVLO feature holds the driver output low, regardless of the status of the input pins. A hysteresis on the UVLO feature prevents glitch when there is noise from the power supply.

The SiLM8260A also monitors the input power supply and there is an internal under voltage lock out protection feature on the VDDI. The driver outputs (OUTA and OUTB) are hold low when the voltage on the VDDI is lower than VUVLO\_VDDI\_R during start up or lower than VUVLO\_VDDI\_F after start up. There is a hysteresis on the VDDI UVLO feature to prevent glitch due the noise on the VDDI power supply.

### **Disable Input Function**

When the DIS is pulled high, the OUTA and OUTB are pulled low regardless of the states of VIA and VIB. When the DIS pin is pulled low, the OUTA and OUTB are allowed for normal operation and controlled by the VIA and VIB.

The DIS input has no effect if VDDI is below its UVLO threshold and OUTA, OUTB remains low. There is an internal pull down resistor on the DIS pin.

### **Control Input and Output Logic**

The VIA and VIB input control the corresponding output channel, OUTA and OUTB. A logic high signal on VIA (VIB) causes the output of OUTA (OUTB) to go high. And a logic low on VIA (VIB) causes the output of OUTA (OUTB) to go low.

The Table 1 shows the relationship between VIA, VIB, DIS, UVLO and Output of OUTA and OUTB.

Table 1. Relationship between Input and Output with VIA, VIB input

| VIA | VIB | DIS | VDDI<br>UVLO | VDDA<br>UVLO | VDDB<br>UVLO | OUTA | OUTB | Note                 |  |

|-----|-----|-----|--------------|--------------|--------------|------|------|----------------------|--|

| Н   | L   | L   | No           | No           | No           | Н    | L    |                      |  |

| L   | Н   | L   | No           | No           | No           | L    | Н    |                      |  |

| L   | L   | L   | No           | No           | No           | L    | L    |                      |  |

| Н   | Н   | L   | No           | No           | No           | L    | L    |                      |  |

| Χ   | Х   | Н   | No           | No           | No           | L    | L    | Device disabled      |  |

| Χ   | Х   | Х   | Yes          | No           | No           | L    | L    | VDDI UVLO active     |  |

| Н   | Х   | L   | No           | No           | Yes          | Н    | L    | VDDB UVLO active     |  |

| L   | Х   | L   | No           | No           | Yes          | L    | L    | . VDDB OVEO active   |  |

| Χ   | Н   | L   | No           | Yes          | No           | L    | Н    | VDDA UVLO active     |  |

| Χ   | L   | L   | No           | Yes          | No           | L    | L    | , vbb/( o veo dolive |  |

#### **Dead-time Program**

There is a dead-time between OUTA and OUTB. The dead-time delay (t<sub>DT</sub>) is programmed by a resistor (R<sub>DT</sub>) connected from the DT input to ground and it can be calculated with below equation.

$$t_{DT}[\text{ns}] \approx 10 \times R_{DT}[\text{k}\Omega]$$

Here, t<sub>DT</sub> is the dead-time delay, R<sub>DT</sub> is the resistance value between DT and ground.

The DT pin can be connected to VDDI or left floating to provide a nominal dead time at approximately 400 ps.

A bypassing capacitor, 2.2nF or greater, is recommended to be put between DT and GNDI to achieve better noise immunity.

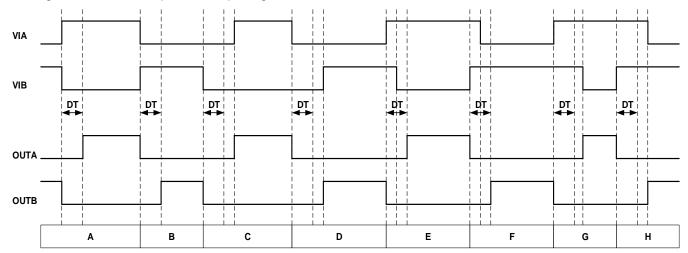

The Figure 6 shows the input and output logic with dead-time in different condition.

Figure 6. Input and output logic with dead-time

Condition A: VIA goes high and VIB goes low. OUTB goes low immediately and OUTA goes high after the programmed dead-time.

Condition B: VIA goes low and VIB goes high. OUTA goes low immediately and OUTB goes high after the programmed dead-time.

Condition C: VIB goes low and VIA still low. OUTB goes low immediately. Since the VIA input dead-time is longer than the programmed dead-time, the OUTA goes high immediately when the VIA input goes high.

Condition D: VIA goes low and VIB still low. OUTA goes low immediately. Since the VIB input dead-time is longer than the programmed dead-time, the OUTB goes high immediately when the VIB input goes high.

Condition E: VIA goes high while VIB and OUTB are still high, the overlap time is shorter than the programmed dead-time. To avoid overshoot, OUTB goes low immediately when the VIA goes high. The OUTA goes high after the programmed dead-time.

Condition F: VIB goes high while VIA and OUTA are still high, the overlap time is shorter than the programmed dead-time. To avoid overshoot, OUTA goes low immediately when the VIB goes high. The OUTB goes high after the programmed dead-time.

Condition G: VIA goes high while VIB and OUTB are still high, the overlap time is longer than the programmed dead- time. To avoid overshoot, OUTB goes low immediately when the VIA goes high. Since the overlap time is longer than the programmed dead-time, the OUTA goes high immediately when the VIB goes low.

Condition H: VIB goes high while VIA and OUTA are still high, the overlap time is longer than the programmed dead-time. To avoid overshoot, OUTA goes low immediately when the VIB goes high. Since the overlap time is longer than the programmed dead-time, the OUTB goes high when the VIA goes low.

#### **Internal Active Miller Clamp**

A Miller clamp circuit integrates in the SiLM8260A which allows the control of the Miller current during a high dV/dt situation and can eliminate the use of a negative supply voltage in most of the applications. During turn off, the gate voltage is monitored through the CLAMPA(B) and the clamp circuit is activated when the voltage on the CLAMPA(B) pin goes below the clamp voltage threshold (2V typical, relative to VEEA(B)). A clamp low sink current is generated when the clamp circuit is activated. The clamp circuit is disabled when the input on signal is triggered again.

#### **Active Output Pulldown**

The active output pulldown feature ensures that the OUTA(B) is clamped to approximately 1.8V higher than VEE2 to ensure safe IGBT off-state during VDDA(B) is open.

### **APPLICATION INFORMATION**

The circuit in Figure 7 shows the typical application circuit for SiLM8260A to driver a typical half bridge configuration which could be used in several popular power converter topologies such as synchronous buck, synchronous boost, half bridge, full bridge, LLC etc. topologies and 3-phase motor drive applications.

Figure 7. Typical Application Schematic

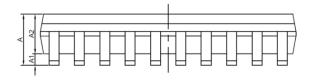

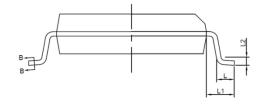

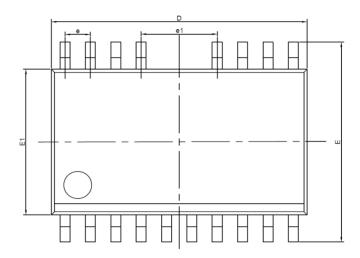

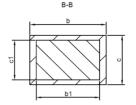

# **PACKAGE CASE OUTLINES**

| Dimension | MIN       | NOM  | MAX  |  |  |

|-----------|-----------|------|------|--|--|

| Α         | -         | -    | 2.65 |  |  |

| A1        | 0.1       | -    | 0.3  |  |  |

| A2        | 2.05      | -    | -    |  |  |

| L         | 0.4       | -    | 1.27 |  |  |

| L1        | -         | 1.4  | -    |  |  |

| L2        | -         | 0.25 | -    |  |  |

| θ         | 0         | -    | 8    |  |  |

| b         | 0.31      | -    | 0.51 |  |  |

| b1        | 0.27      | -    | 0.48 |  |  |

| С         | 0.1       | -    | 0.33 |  |  |

| c1        | 0.1       | -    | 0.3  |  |  |

| D         | -         | 12.8 | -    |  |  |

| E         | -         | 10.3 | -    |  |  |

| E1        | -         | 7.5  | -    |  |  |

| е         | 1.27BASIC |      |      |  |  |

| e1        | 3.81BASIC |      |      |  |  |

| Unit : mm |           |      |      |  |  |

|           |           |      |      |  |  |

Figure 8. SOP18W Package Outline Dimensions

## **REVISION HISTORY**

Note: page numbers for previous revisions may differ from page numbers in current version

| Page or Item                  | Subjects (major changes since previous revision)                                                                     |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Rev 1.0 datasheet: 2023-10-15 |                                                                                                                      |  |  |  |

| Whole document                | Initial datasheet release                                                                                            |  |  |  |

| Rev 1.1 datasheet: 2024-11-28 |                                                                                                                      |  |  |  |

| Page 12                       | Update the parameters: t <sub>PLH</sub> , t <sub>PHL</sub> , t <sub>PW</sub> , t <sub>DM</sub> and t <sub>DT</sub> . |  |  |  |

| Rev 1.2 datasheet: 2025-05-20 |                                                                                                                      |  |  |  |

| Page 12                       | Add the parameter t <sub>PW_MIN</sub>                                                                                |  |  |  |